GC7232----USB 转串口芯片

## <u>目录</u>

| 1. | 概述    |                                   | 4  |

|----|-------|-----------------------------------|----|

| 2. | 特点    |                                   | 4  |

|    | 2.1.  | 硬件特征                              | 4  |

|    | 2.2.  | 实际串行通道驱动器                         | 5  |

|    | 2.3.  | D2XX (USB 直接驱动器 + DLL S/W 接口)     | 5  |

|    | 2.4.  | 应用领域                              | 6  |

| 3. | 部分特   | ·点的着重介绍                           | 7  |

|    | 3.1.  | 集成电路工作复位(POR)电路                   | 7  |

|    | 3.2.  | 集成电路 RCCLK 电路介绍                   | 7  |

|    | 3.3.  | UART 接口和控制信号集成转换                  | 7  |

|    | 3.4.  | 针对 USB 总线功率器件和高电流器件进行了功率管理控制方面的改善 | 7  |

|    | 3.5.  | 比较低的暂停电流                          | 7  |

|    | 3.6.  | 支持 USB 同步传输                       | 7  |

|    | 3.7.  | 接收的缓冲时间可编程                        | 8  |

|    | 3.8.  | TXDEN 计时固定                        | 8  |

|    | 3.9.  | 放宽 VCC 退耦                         | 8  |

|    | 3.10. | 改善预定标器的刻度                         | 8  |

|    | 3.11. | 位邦模式                              | 8  |

|    | 3.12. | 预定标器除以 1 固定                       | 8  |

|    | 3.13. | 较少的外部支持元件                         | 8  |

|    | 3.14. | 支持 EEPROM 扩展                      | 9  |

|    | 3.15. | USB 2.0(全速选项)                     | 9  |

|    | 3.16. | 无 EEPROM 时支持多个器件                  | 9  |

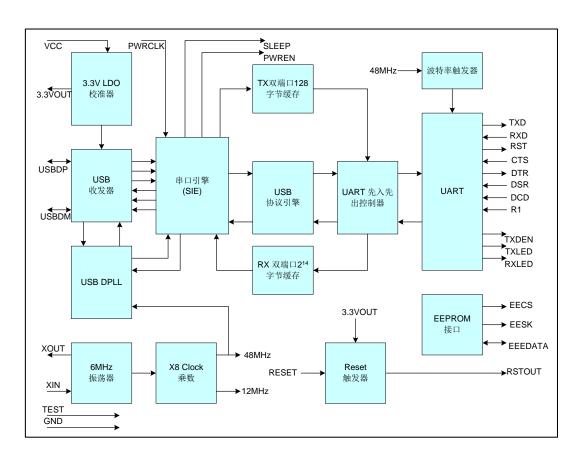

| 4. | 方块图   | 简介                                | 10 |

|    | 4.1.  | 3.3V LDO 校准器                      | 10 |

|    | 4.2.  | USB 收发器                           | 10 |

|    | 4.3.  | USB DPLL                          | 10 |

|    | 4.4.  | 6MHz 振荡器                          | 11 |

|    | 4.5.  | X8 clock 乘数                       | 11 |

|    | 4.6.  | 串行接口引擎(SIE)                       | 11 |

|    | 4.7.  | USB 协议引擎                          | 11 |

|    | 4.8.  | TX 两端口 128 字节缓存                   | 11 |

|    | 4. 9. | RX 两端口 2 <sup>14</sup> 字节缓存       | 11 |

|    | 4.10. | UART 先进先出控制器                      | 11 |

|    | 4.11. | UART                              | 11 |

|    | 4.12. | 波特率发生器                            | 12 |

|    | 4.13. | RESET 发生器                         | 12 |

|    | 4.14. | EEPROM 接口                         | 12 |

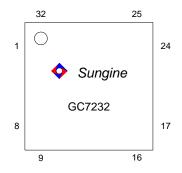

| 5. | 引脚介   | 绍                                 | 12 |

|    | 5.1.  | 芯片封装外观                            | 12 |

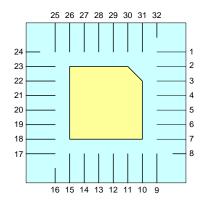

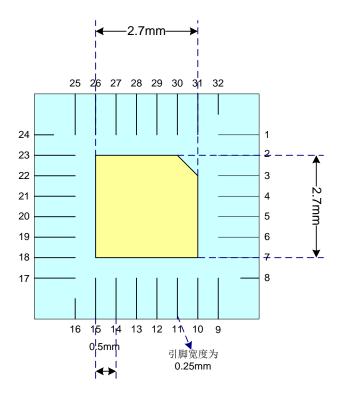

|     | 5.2.  | 芯片封装引脚示意图                               | 13 |

|-----|-------|-----------------------------------------|----|

|     | 5.3.  | 芯片引脚原理图示                                | 13 |

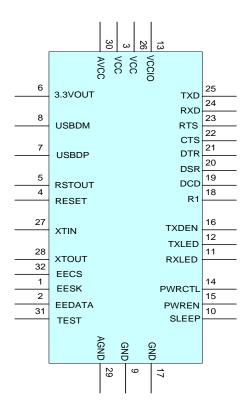

| 6.  | 引脚信   | 号描述                                     | 14 |

|     | 6.1.  | UART 接口                                 | 14 |

|     | 6.2.  | USB 接口                                  | 14 |

|     | 6.3.  | EEPROM 接口                               | 14 |

|     | 6.4.  | 电源控制模组                                  | 15 |

|     | 6.5.  | 多信号模组                                   | 16 |

|     | 6.6.  | 电源和接地引脚                                 | 16 |

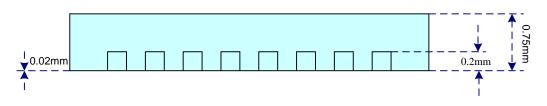

| 7.  | 封装尺   | ਰ 대示意图                                  | 18 |

| 8.  |       | ī列举                                     |    |

| 9.  | 交流规   | 见格参数表(环境温度为 0~70℃)                      | 20 |

|     | 9.1.  | 操作电压和电流                                 |    |

|     | 9.2.  | VCCIO=5.0V 时, UART 输入输出引脚的参数特性          |    |

|     | 9.3.  | VCCIO=3.0~3.6V 时, UART 输入输出引脚的参数特性      |    |

|     | 9.4.  | XIN/XOUT 引脚特性                           | 21 |

|     | 9.5.  | RESET,TEST,EECS,EESK,EEDATA 引脚特性        | 21 |

|     | 9.6.  | RSTOUT 引脚特性                             | 22 |

|     | 9.7.  | USB 输入输出引脚特性                            |    |

| 10. | 器     | 件配置列举                                   |    |

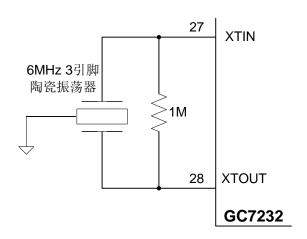

|     | 10.1. | 引脚陶瓷振荡器配置                               |    |

|     | 10.2. | 晶体或者 2 引脚陶瓷振荡器配置                        |    |

|     | 10.3. | EEPROM 配置                               |    |

| 11. | U     | SB 总线电源和本身电源配置                          | 25 |

|     | 11.1. | USB 总线电源配置                              |    |

|     | 11.2. | USB 自身功率配置                              | 26 |

| 12. | U     | ART 接口配置                                | 27 |

|     | 12.1. | USB 与 RS232 转换器配置                       | 27 |

|     | 12.2. | USB 与 RS422 转换器配置                       | 28 |

|     | 12.3. | USB 与 RS485 转换器配置                       |    |

| 13. | L     | ED 接口                                   |    |

|     | 13.1. | 双 LED 配置                                |    |

|     | 13.2. | , , , , , , , , , , , , , , , , , , , , |    |

| 14. | 3.    | 3V 逻辑接口                                 |    |

|     | 14.1. | 总线功率电路带有 3.3V 逻辑驱动/电压源                  |    |

|     | 14.2. |                                         |    |

| 15. | 电     | · 源开关                                   |    |

|     | 15.1. |                                         |    |

| 16. |       | 「货信息                                    |    |

| 17. | -     | C档修改记录                                  |    |

| 18. | 文     | [档信息                                    | 34 |

# USB 转串口芯片

## 1. 概述

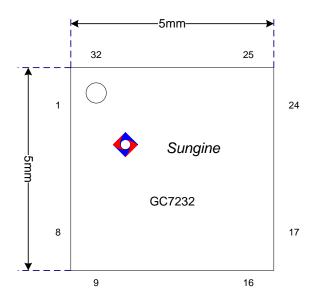

GC7232 是一款 USB 转串口芯片,采用 5\*5mm 无铅 QFN32 包装技术,引脚具有高度兼容性,设计简单,升级方便,应用领域广泛。

# 2. 特点

## 2.1. 硬件特征

- ◆ 单芯片数据与异步串行数据之间数据的交换

- ◆ 全握手和调制解调器接口信号

- ◆ UART I/F,支持 7/8 位数据, 1/2 个停止位,奇校验/偶校验/标志/空位/无奇偶校验

- ◆ TTL 数据速率 300~3M 波特

- ◆ RS232 数据速率 300~1M 波特

- ◆ R422/RS485 数据速率 300~3M 波特

- ◆ 对于大量数据传输,有接收缓存 384 位,发射缓存 128 位

- ◆ 缓冲区缓冲时间可调整

- ◆ 全辅助硬件,或者 X-on/X-off 握手

- ◆ 内置支持事件符号和换行条件

- ◆ RS485 发射缓存可自动控制

- ◆ 支持 USB 暂停,可通过"sleep"和"R1"引脚实现重新开始

- ◆ 通过 "power" 引脚支持高功率 USB 总线功率器件

- ◆ UART 集成转换,控制信号用于连接 5V 和 3.3V 逻辑

- ◆ USB 接口集成了 3.3V 的校准器

- ◆ 集成了工作复位电路

- ◆ 集成了 6MHz~48MHz 时钟乘数 PLL

- ◆ USB 主体或者同步数据传输模式

- ◆ 4.35V~5.25V 信号供应操作

- ◆ UHCI/OHCI/EHCI 主机控制器兼容

- ◆ USB1.1/USB2.2 兼容

- ◆ USB 的 VID/PID/序列号/产品描述字符串在另外一个 EEPROM

- ◆ 通过 USB 可实现对 EEPROM 的编程

- ◆ 采用 5\*5mm 无铅 QFN32 包装技术

## 2.2. 实际串行通道驱动器

- Windows 98 and Windows 98 SE

- ◆ Windows 2000 / ME / 服务器 2003 / XP

- ◆ Windows XP 64 位

- ◆ 嵌入式 Windows XP

- ♦ Windows CE 4.2

- ♦ MAC OS-8 and OS-9

- ♦ MAC OS-X

- ◆ Linux 2.40 及以上

## 2.3. D2XX (USB 直接驱动器 + DLL S/W 接口)

Windows 98 and Windows 98 SE

- ◆ Windows 2000 / ME / 服务器 2003 / XP

- ◆ Windows XP 64 位

- ◆ 嵌入式 Windows XP

- ♦ Windows CE 4.2

- ◆ Linux 2.40 及以上

### 2.4. 应用领域

- ◆ USB 和 RS232 串口之间的转换

- ◆ USB 和 RS422/RS485 之间的转换

- ◆ 升级 RS232 外围到 USB

- ◆ 蜂窝式无线通讯系统和无线系统之间的数据传输通道和接口

- ◆ 基于 MCU 的 USB 接口设计

- ◆ USE 和低带宽视频数据之间的传输

- ◆ PDA 和 USB 之间的数据传输

- ◆ USB 只能读卡器

- ◆ 机顶盒的 USB 接口

- ◆ USB 硬件调制解调器

- ◆ USB 无线调制解调器

- ◆ USB 测量仪器仪表

- ◆ USB 条形码读取器

# 3. 部分特点的着重介绍

## 3.1. 集成电路工作复位(POR)电路

◆ 这个设备目前包含一个内部工作复位的功能。现有的"RESET"引脚主要是在需要的情况下,维持允许外部逻辑实现器件的复位状态,但是在很多应用中,该引脚都被简单的硬连接到 Vcc。 另外,一个新的复位输出引脚"RSTOUT"为了允许新的 POR 电路来给外围的 MCU 和其他器件提供一个稳定的复位状态。

## 3.2. 集成电路 RCCLK 电路介绍

◆ RCCLK 电路可以保证振荡器和时钟乘数 PLL 的频率保持稳定,从而提供稳定的时钟给器件内部。在正常情况下,只需将"test"引脚接 GND 即刻。

### 3.3. UART 接口和控制信号集成转换

◆ 独立的 "VCC-IO" 引脚允许器件直接接到 3.3V 电源, 无需其他外围设备。

# 3.4. 针对 USB 总线功率器件和高电流器件进行了功率管理控制 方面的改善

◆ USB 插入器件之后,可通过 "SLEEP"和 "RESET"传递功率控制信号。在实际应用过程中,当需要外围电路的功率开关时,引脚 "PWREN"可以直接驱动一个晶体管或者 P 通道 MOS 管。当功率关断时("PWREN"引脚处于高电平状态)基于 EEPROM 的选项使得器件能够缓和的降低 UART 接口线。在这个模式下,外围电路的剩余电压流向 GND。电源切断时,可以保证外围电路受控于 "PWREN"引脚,当电源修复时,也可以稳定的修复。

## 3.5. 比较低的暂停电流

◆ 片内集成 RCCLK 以及内部设计的一些改善,使得 USB 在暂停模式下耗电电流在 200μA 以下,这样一来,对外围器件的要求就变得比较宽松,因为 USB 的暂停电流要求在 500μA 以内。

## 3.6. 支持 USB 同步传输

◆ 对于数据传输时间不需要保证的情况,利用 USB 本身作为数据传输的途径是最佳的选择。 但是对于类似视频数据这类对数据传输顺序有潜在要求的情况,可以通过器件内 EEPROM 的位选项实现 USB 同步传输。

### 3.7.接收的缓冲时间可编程

◆ 接收的缓冲时间主要是来清理上次接收后残存的数据,这个时间可以通过编程 USB (1ms 以内),时间范围在 1ms~255ms 之间,这样一来,对于数据比较少的数据传输,可以尽可能的优化交易的进行时间,缩短数据接收的时间。

### 3.8. TXDEN 计时固定

◆ 目前对 TXDEN 计时固定来消除外部延迟,在发射失败的情况下,TXDEN 目前可以正确的工作。

## 3.9. 放宽 VCC 退耦

◆ 该器件目前在芯片上集成了 VCC 退耦模块。因此,并没有淘汰外部设备退耦电容的需求。 这个特点标志着降低 PCB 设计对 FCC,CE 以及其他 EMI 相关规格的要求的难度。

### 3.10. 改善预定标器的刻度

◆ 之前的版本支持除以(n+0)/(n+0.125)/(n+0.5)。这款芯片在之前的基础之上,又增加了 (n+0.625)/(n+0.75)/(n+0.875)。其中 n 为 2~16384(214) 之间的整数。这样一来,提高了 波特率的精确性,同时产生了以前版本无法产生的波特率。

## 3.11. 位邦模式

◆ 这是这款芯片的一大亮点。在位邦模式下,UART接口的 8 个控制线可以再 UART接口模式和 8 位并行端口之间转换。数据包可以被发送到设备,从而以一定的比率发送到接口,这个比率由预定标器来设定。这样一来也允许器件单机本身可以被用来当做一个通用的双接口控制器,比如灯光控制器,延迟控制器,开关控制器,一起其他有可能存在的比较有趣的情况。例如,卖房可以提供这款芯片用来连接器件和 SRAM结构的 FPGA。FPGA在升高情况下没有配置。电脑上的应用软件可以使用位邦模式下载配置到可以定义硬件功能的 FPGA,在FPGA器件有了GC7232的配置之后,可以转回到 UART接口模式下,允许可编程的 FPGA器件通过 USB与电脑实现信息交流。这样就允许用户创建一类的在应用软件控制下的外围电路。可以通过改变 FPGA配置的数据文件来很简单的实现 FPGA的升级或者全部更换。应用领域的应用笔记,软件和开发模块可以与双竞科技有限公司索取。

### 3.12. 预定标器除以 1 固定

◆ 预定标器数值为1时,结果是200,0000波特,为0时为300,0000波特,不支持非整数除法。

## 3.13. 较少的外部支持元件

◆ 在 RCCLK 网络内置之后,大部分用户需要一个外部复位电路,我们同事也省略了 EECS 的

100k的拉起操作,仅需要 6MHz的操作即可。GC7232 在没 EEPROM/EECS/EESK/EEDATA配置的情况下可以被设置成无连接状态。对于复位时间比较长的电路,不再需要外部晶体管电路,将 USB 的 1.5k 的上拉电阻连接到"RSTOUT"引脚即可。注意:"RSTOUT"工作电压为 3.3V,不是 5V。这是首选的配置。

## 3.14. 支持 EEPROM 扩展

◆ GC7232 的 EEPROM 有 93C56 和 93C66 两种类型。器件不可以利用额外的空间,然而在 GC7232 复位的同事,外部的 MCU 和逻辑可以使用。

#### 3.15. USB 2.0 (全速选项)

◆ 新的 EEPROM 基本选项允许 GC7232 返回 USB 2.0 的描述, USB 1.0 则不可以。注意:器件必须是 USB 2.0 全速(120Mb/s)器件,相对与 USB 2.0 高速器件(480Mb/s)。

#### 3.16. 无 EEPROM 时支持多个器件

◆ 当器件没有附带 EEPROM 时,GC7232 不会给出 USB 表述的串联码。这样允许多个器件同时连接到电脑。但是,我们还是推荐连接 EEPROM,因为没有串联码,器件只能通过在 USB 上的端口来被识别,而终端用户重新插到其他端口的动作会改变器件在 USB 上的端口。

# 4. 方块图简介

## 4.1.3.3V LDO 校准器

◆ 3.3V 校准器产生 3.3V 的参考电压,来触发 USB 收发器的输出缓存。3.3VOUT 端连接一个 退耦电容。同样该模块可以给 Reset 触发器提供 3.3V 的参考电源。与其说这个模块的主要 功能是给外部逻辑提供电源,还不如说是给 USB 收发器和 Reset 触发器提供电源。但是,如果外部电路需要 5mA 以内的电流时,该模块也可以通过 3.3VOUT 端提供 3.3V 电源。

## 4.2.USB 收发器

◆ 该模块提供 USB1.0/USB2.0 与 USB 电缆之间的全速物理接口。输出驱动器提供 3.3V 的控制信号速率,同时一个不同的接收器和两个终端接收器提供给 USB 数据、SEO 和 USB 复位条件的探测。

#### 4.3. USB DPLL

◆ USB DPLL 与 USB 新进的 NRZI 数据锁定,提供独立的恢复时钟和数据信号给 SEI 模块。

### 4.4.6MHz 振荡器

◆ 该模块通过外置的 6MHz 的共振器产生 6MHz 的参考时钟,提供给 x8 clock 乘数模块。

#### 4.5. X8 clock 乘数

◆ 该模块将 6MHz 模块输入的参考时钟转换成 12MHz 的参考时钟,提供给 SIE、USB 协议引擎和 UART 先进先出控制器模块。也可以产生 48MHz 的参考时钟,提供给 USB DPLL 和波特率触发器模块。

### 4.6. 串行接口引擎 (SIE)

◆ 该模块中进行 USB 数据串行和并行的互转。根据 USB2.0 的说明,主要执行 USB 数据流的 位填充和位非填充、CRC5/CRC16 的产生和检查。

### 4.7. USB 协议引擎

◆ 该模块主要管理期间 USB 终点的数据流。操作低等级的 USB 控制端和控制 UART 有用参数的指令的 USB 协议要求。

## 4.8. TX 两端口 128 字节缓存

◆ USB 输出数据存入该模块,并且在 UART 先进先出控制器模块的控制下移到 UART 发射控制器中。

#### 4.9. RX 两端口 2<sup>14</sup>字节缓存

◆ 当 USB 要求从终端器件输入数据时, UART 接受触发器的数据将会通过 SIE 由转移, 在转移之前,数据将会暂时存储在该模块。

### 4.10. UART 先进先出控制器

◆ 该模块主要是控制各个缓存区和收发器之间的数据传输。

#### 4.11. UART

◆ UART 可在 RS232/RS422/RS485 接口执行 7/8 位的并行和串行数据的互转。UART 支持包括 RTS/CTS/DSR/DTR/DCD 和 RI 的控制信号。UART 提供一个发射器使能(TXDEN)控制信号来协助与 RS485 接受器的连接。UART 支持 RTS/CTS,DSR/DTR,X-ON/X-OFF 握手选项。握手要求硬件操作,并且短时间内做出响应。UART 也支持 RS232 的间歇设置和检测条件。

## 4.12. 波特率发生器

◆ 该模块输入 48MHz 的参考时钟,可以向 UART 输入 x16 的时钟。该模块由 14 为的预定标器和 3 位注册位组成,3 位注册位可提供波特率的精微调(通常是除以正小数)。UART 的波特率可通过编程来确定,一般在 183 波特到 300,0000 波特之间。

### 4.13. RESET 发生器

◆ 电源上拉时,RESET 发生器可以给器件内部电路提供稳定的加电复位。一对额外的"RESET" "RSTOUT"引脚主要是为了实现不同器件分别复位。在复位期间,"RESET"低电平有效,否则会被板上的校准器产生的 3.3V 电压关断。"RSTOUT"可直接控制 USB 上 1.5k 上拉,因为需要 USB 列举时间延迟。同样可以用来实现其他器件的复位。在 VCC 上升到 3.5V,器件的振荡器开始工作,"RESET"为高电平之后,"RSTOUT"将保持大约 5ms 的高阻状态。除非有外部逻辑要求器件复位或者外部发生器复位,"RESET"应该接到 VCC。

### 4.14. EEPROM 接口

- ◆ 虽然 GC7232 可以在没有 EEPROM 的情况下工作,可以用一个 93C46/93C56/93C66 的 EEPROM 来定制 USB 的 VID/PID/序列号/产品描述/功率描述给制造商。EEPROM 可控制的 参数还包括微激活,同步传送模式,电源关断时软下拉和 USB2.0 描述符模式。

- ◆ EEPROM 应该有 16 位的配置,比如微晶片 93LC46B 或者同类具有在 VCC=4.5V~5.25V 时有 1 M/s 时钟率的芯片。EEPROM 可以实现板上编程。这样一来就可以在 PCB 板上焊接一个空件,编程这部分为制造和测试过程中的一部分。

- ◆ 在没有 EEPROM 的情况下,GC7232 可以使用其内建默认的 VID/PID/产品说明/功率说明。 这种情况下,该器件的 USB 描述符将不会出现序列号。

# 5. 引脚介绍

### 5.1. 芯片封装外观

## 5.2. 芯片封装引脚示意图

## 5.3. 芯片引脚原理图示

# 6. 引脚信号描述

## 6.1. UART 接口

| 引脚 | 信号    | <br>  引脚类型<br> | 描述                             |

|----|-------|----------------|--------------------------------|

| 25 | TXD   | 输出             | 发射异步信号                         |

| 24 | RXD   | 输入             | 接收异步信号                         |

| 23 | RTS   | 输出             | 请求发送控制输出/握手信号                  |

| 22 | CTS   | 输入             | 清除发送控制输出/握手信号                  |

| 21 | DTR   | 输出             | 控制输入/握手信号数据终端准备                |

| 20 | DSR   | 输入             | 控制输入/握手信号数据装置准备                |

| 19 | DCD   | 输入             | 数据载体检测控制输入                     |

| 18 | R1    | 输入             | 报警器控制输入。当 EEPROM 的微激活选项有效,R1 低 |

| 10 | K1    | 199 八          | 电平可以重新启动暂停的电脑 USB 用户控制器。       |

| 16 | TXDEN | 输出             | 允许发射数据给 RS485                  |

## 6.2. USB 接口

| 引脚 | 信号    | 引脚类型  | 描述                                         |

|----|-------|-------|--------------------------------------------|

| 7  | USBDP | 输出/输入 | 正 USB 数据信号( 要求 3.3VOUT 或者 RSTOUT 1.5k 的上拉) |

| 8  | USBDM | 输出/输入 | 负 USB 数据信号                                 |

## 6.3. EEPROM 接口

|--|--|--|

|    | EECS   | 输出/输入        | EEPROM <b>片选引脚。在</b> EECS 和 GND 之间接 10k 电阻来进行 48MHz |

|----|--------|--------------|-----------------------------------------------------|

| 32 |        |              | 的操作。6MHz 操作时,则不需要接电阻。在器件复位的过程                       |

|    |        |              | 中为三态。                                               |

|    | EESK   | 输出           | EEPROM 时钟信号引脚。在期间复位过程中为三态,其余情                       |

| 1  |        |              | 况下为悬空状态。EESK 添加 10k 的下拉电阻会导致 GC7232                 |

| 1  |        |              | 使用 USB 产品 ID 为 6004 来取代 ID 为 6001 的。其他 USB          |

|    |        |              | 器件的描述将不被改变。                                         |

|    | EEDATA | EEDATA 输出/输入 | EEPROM 数据输入输出接口。通过一个 2.2k 的电阻可以直接                   |

| 2  |        |              | 和输入输出接口连接。也可以在数据输出端口和 VCC 之间加                       |

| 2  |        |              | 一个 10k 的电阻来进行校正操作。在器件复位的过程中为三                       |

|    |        |              | 态。                                                  |

## 6.4. 电源控制模组

| 引脚 | 信号     | 引脚类型     | 描述                                 |

|----|--------|----------|------------------------------------|

|    |        |          | USB 暂停时为低电平。在设计 RS232 和 USB 转换器时,通 |

| 10 | SLEEP  | 输出       | 常用来关断外部晶体管到 RS232 之间的转换器集成电路的电     |

|    |        |          | 源。                                 |

|    | PWREN  |          | 器件和 USB 连接之后为低电平,USB 暂停时为高电平。可以    |

| 15 |        | PWREN 输出 | 用 P 沟道逻辑级晶体管开关来控制外部逻辑电源。当以这种       |

|    |        |          | 方式用该引脚时,可以开启 EEPROM 接口下拉的选项。       |

| 14 | PWRCTL | 输入       | 低电平为总线电源,高电平(连接到 VCCIO)为自身电源。      |

# 6.5. 多信号模组

| 引脚 | 信号              | 引脚类型       | 描述                                  |  |

|----|-----------------|------------|-------------------------------------|--|

| 4  | タ<br>4 RESET 輸入 |            | 外部器件可以通过该引脚对 GC7232 进行复位。无需复位时,     |  |

| 4  | KESE I          | 湘 <i>人</i> | 将该引脚连接到 VCC 即可。                     |  |

|    |                 |            | 内部复位发生器输出引脚。VCC 大于 3.5V,内部时钟开启之     |  |

| 5  | RSTOUT          | UT 输出      | 后,该引脚会维持 5ms 的高阻状态,然后会将内部发生器的       |  |

| 3  | K31001          |            | 输出嵌制在 3.3V。RESET 低电平会强制 RSTOUT 低电平。 |  |

|    |                 |            | RSTOUT 不受 USB 总线复位的影响。              |  |

| 12 | TXLED           | 开路         | LED 驱动引脚。USB 发射数据时为低电平。             |  |

| 11 | RXLED           | 开路         | LED 驱动引脚。USB 接收数据时为低电平。             |  |

|    | XTIN            | N 输入       | 6MHz 晶体振荡器输入引脚。如果需要,该引脚也可以被外接       |  |

| 27 |                 |            | 6MHz 时钟驱动。注意:该引脚的开关阈值为 VCC/2,所以     |  |

| 27 |                 |            | 当外部器件驱动该引脚时,驱动源必须在 5V CMOS 的级别,     |  |

|    |                 |            | 或者交流电的中心值必须达到 VCC/2。                |  |

| 28 | XTOUT           | 输出         | 6MHz 晶体振荡器输出引脚。USB 暂停期间,该引脚停止震      |  |

| 28 | AIUUI           | 初山         | 动,所以如果该引脚连接外部时钟时,要倍加小心。             |  |

| 31 | TEST            | 输入         | 测试引脚。操作时,必须接 GND。                   |  |

## 6.6. 电源和接地引脚

| 引脚 | 信号      | 引脚类型 | 描述                             |

|----|---------|------|--------------------------------|

| 6  | 3.3VOUT | 输出   | LDO 发生器 3.3V 输出引脚。在仅仅器件引脚附近,该引 |

| 行退耦。这样    |

|-----------|

|           |

| JSB 收发器和  |

| F 5mA 的电流 |

|           |

| UART 接口。  |

| 口,引脚      |

| ,当连接外部    |

| / 电源发生器。  |

| 辑接口时,连    |

| 该引脚到 VCC  |

|           |

|           |

|           |

|           |

| 7         |

注意:在期间复位期间,这些引脚呈三态,但是通过 200k 的上拉电阻与 VCC 连接。

# 7. 封装尺寸示意图

◆ GC7232 封装技术为 QFN32 无铅包装。5mm\*5mm 的尺寸,无伸出引脚,对于那些对芯片面积要求比较高的项目,该封装是非常理想的选择。上面展示的示意图,尺寸均以毫米为单位。

# 8. 极限值列举

根据极限系统(IEC60134),以下列举出 GC7232 工作的极限值。超过极限值工作,会导致器件永久性损伤。

| 参数                              | 极限值               | 单位 |

|---------------------------------|-------------------|----|

| 存储温度                            | -65°C~+150°C      | °C |

| 在没有包装袋,工厂周围温度为 30℃,60%的相对湿度下的最低 | 192 小时*           |    |

| 使用寿命                            |                   |    |

| 供给电源的环境温度                       | 0°C~+70°C         | °C |

| 35℃情况下的可靠度                      | 24748 小时 約为 28    |    |

|                                 | 年                 |    |

| VCC 电源电压                        | -0.5~+6           | V  |

| USBDP/USBDM 直流输入电压              | -0.5~+3.8         | V  |

| 双向高阻抗直流输入电压                     | -0.5~+ ( VCC+0.5) | V  |

| 其余输入端口直流输入电压                    | -0.5~+ ( VCC+0.5) | V  |

| 输出端口直流输出电流                      | 24                | mA |

| 双向低阻抗直流输出电流                     | 24                | mA |

| VCC=5.25V 时的消耗功率                | 500               | mW |

| I<1 μA 时,人体模式静电放电电压             | ±3000             | V  |

| Vimax=±10V,并维持 10ms 时,栓锁电流 | ±200 | mA |

|----------------------------|------|----|

|                            |      |    |

\*注意:如果器件脱离包装存储的时间大于这个时间,那么在使用之前应该进行烘烤。需要在 110℃ 的环境下倾斜烘烤 8 到 10 小时。

# 9. 交流规格参数表(环境温度为 0~70℃)

### 9.1. 操作电压和电流

| 参数   | 描述               | 最小值   | 典型值 | 最大值   | 单位 | 测试条件    |

|------|------------------|-------|-----|-------|----|---------|

| VCC1 | VCC 电压源          | 4. 35 | 0   | 5. 25 | V  |         |

| VCC2 | VCCIO <b>电压源</b> | 3. 0  | -   | 5. 25 | V  |         |

| ICC1 | 电流源              | _     | 25  | _     | mA | 正常操作    |

| ICC2 | 电流源              | _     | 180 | 200   | 微安 | USB 暂停* |

\*注意:电流源不包括 USBDP 外部上拉电阻消耗的 200 微安。

## 9.2. VCCIO=5.0V 时, UART 输入输出引脚的参数特性

| 参数   | 描述     | 最小值  | 典型值  | 最大值  | 单位 | 测试条件             |

|------|--------|------|------|------|----|------------------|

| Voh  | 高电压输出  | 3. 2 | 4. 1 | 4. 9 | V  | Isource=2mA      |

| Vol  | 低电压输出  | 0.3  | 0.4  | 0.6  | V  | Isink=2mA        |

| Vin  | 输入开关阈值 | 1.3  | 1. 6 | 1.9  | V  | 内部 200k 上拉电<br>阻 |

| VHys | 输入开关延迟 | 50   | 55   | 60   | 毫Ⅴ |                  |

## 9.3. VCCIO=3.0~3.6V 时, UART 输入输出引脚的参数特性

| 参数   | 描述     | 最小值  | 典型值 | 最大值  | 单位 | 测试条件         |

|------|--------|------|-----|------|----|--------------|

| Voh  | 高电压输出  | 2. 2 | 2.7 | 3. 2 | V  | Isource=1mA  |

| Vol  | 低电压输出  | 0.3  | 0.4 | 0.5  | V  | Isink=2mA    |

| Vin  | 输入开关阈值 | 1.0  | 1.2 | 1.5  | V  | 内部 200k 上拉电阻 |

| VHys | 输入开关延迟 | 20   | 25  | 30   | mV |              |

## 9.4.XIN/XOUT 引脚特性

| 参数  | 描述     | 最小值  | 典型值 | 最大值  | 单位 | 测试条件      |

|-----|--------|------|-----|------|----|-----------|

| Voh | 高电压输出  | 4. 0 | _   | 5. 0 | V  | Fosc=6MHz |

| Vol | 低电压输出  | 0. 1 | _   | 1.0  | V  | Fosc=6MHz |

| Vin | 输入开关阈值 | 1.8  | 2.5 | 3. 2 | V  |           |

## 9.5. RESET,TEST,EECS,EESK,EEDATA 引脚特性

| 参数   | 描述     | 最小值  | 典型值  | 最大值 | 单位 | 测试条件        |

|------|--------|------|------|-----|----|-------------|

| Voh  | 高电压输出  | 3. 2 | 4. 1 | 4.9 | V  | Isource=2mA |

| Vol  | 低电压输出  | 0.3  | 0.4  | 0.6 | V  | Isink=2mA   |

| Vin  | 输入开关阈值 | 1.3  | 1.6  | 1.9 | V  | *           |

| VHys | 输入开关延迟 | 50   | 55   | 60  | 毫Ⅴ |             |

\*注意: EECS,EESK 和 EEDATA 引脚和 VCC 之间有一个 200k 的内部上拉电阻。

## 9.6. RSTOUT 引脚特性

| 参数  | 描述    | 最小值  | 典型值 | 最大值 | 单位 | 测试条件        |

|-----|-------|------|-----|-----|----|-------------|

| Voh | 高电压输出 | 3. 0 | -   | 3.6 | V  | Isource=2mA |

| Vol | 低电压输出 | 0.3  | -   | 0.6 | V  | Isink=2mA   |

## 9.7. USB 输入输出引脚特性

| 参数    | 描述                | 最小值 | 典型值 | 最大值  | 单位 | 测试条件                      |

|-------|-------------------|-----|-----|------|----|---------------------------|

| UVoh  | 高电压静态输出           | 2.8 |     | 3. 6 | V  | RI=1.5K 到 3.3VOUT 端 D+ )  |

|       |                   |     |     |      |    | RI=1.5K 到 GND 端(D-)       |

| UVo1  | <br>  低电静态压输出<br> | 0   |     | 0. 3 | V  | RI=1.5K 到 3.3VOUT 端( D+ ) |

|       |                   |     |     |      |    | RI=1.5K 到 GND 端(D-)       |

| UVse  | Rx 单边有效阈          | 0.8 |     | 2. 0 | V  |                           |

|       | 值                 |     |     |      |    |                           |

| UCom  | 差分共模              | 0.8 |     | 2. 5 | V  |                           |

| UVDif | 差分输入灵敏度           | 0.2 |     |      | V  |                           |

| UDrvZ | 驱动输出阻抗            | 29  |     | 44   | 欧姆 | *                         |

\*注意:驱动输出阻抗包括 USBDP 和 USBDM 引脚外部串联的 27R 电阻。

# 10. 器件配置列举

#### 10.1. 引脚陶瓷振荡器配置

- ◆ 上图展示了如何将 3 引脚 6MHz 的陶瓷振荡器与 GC7232 连接。3 引脚陶瓷振荡器有内建电容,因此不需要外接电容。这样就减少了外接电路的成本。3 引脚陶瓷振荡器的精度是±0.1%,专门为 USB 全速运行软件设计。在 XTIN 和 XTOUT 之间连接 1M Ω 的电阻,主要是为了确保 3 引脚陶瓷振荡器的精度。

- ◆ 其他陶瓷振荡器的精度一般在±0.5%,技术上和 USB 的规格不相符合,但是上述方案在实际操作中可以顺利的工作。

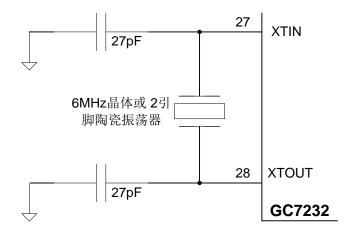

### 10.2. 晶体或者 2 引脚陶瓷振荡器配置

◆ 上图展示了如何连接 6MHz 晶体或 2 引脚陶瓷振荡器。在这种情况下,因为没有内部电容, 所以需要外接电容,具体连接如图所示。虽然绝大多数晶体或者 2 引脚陶瓷振荡器都可以连接 27pF 的电容,但是具体电容的大小需要根据制造商的推荐自行选择。如果使用晶体,使用

平行切割类型。如果使用2引脚陶瓷振荡器,要根据前期频率精度的记录而定。

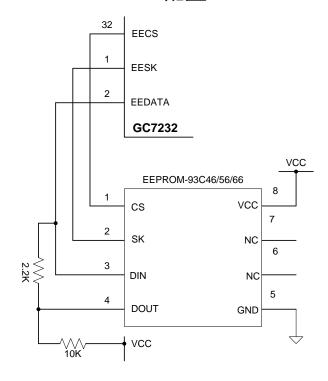

#### 10.3. EEPROM 配置

- ◆ 上图展示了如何连接 GC7232 和 EEPROM(93C46/56/66),各引脚连接如图所示。有个潜在条件,EEPROM 的引脚 DOUT 可以和 GC7232 的引脚 EEDATA 同时驱动。在这个条件下,为了预防潜在的数据冲击,EEDATA 和 DOUT 之间连接了 2.2K 的电阻。

- ◆ 电源复位或者 USB 复位之后,GC7232 会对 EEPROM 进行扫描,去检测 EEPROM 是否连接器件,以及器件里的数据是否有效。如果 EEPROM 连接了器件,并且器件的数据有效,那么 GC7232 会使用该数据,否则 GC7232 会使用其内部默认的数据。如果 GC7232 给 EEPROM 下达有效指令,EEPROM 通过 DOUT 低电平来识别指令。为了检查 DOUT 的电平条件,需要外接 10k 电阻到 VCC 端。如果并未发生指令认证,在这期间 DOUT 会被 10k 电阻提升电位,同时,期间会检测到无效的指令或者为连接 EEPROM。

- ◆ 市面上有两种类型的 EEPROM,分别是 16 位宽和 8 位宽。GC7232 可以与 16 位宽的 EEPROM 配置。比如微晶片 93LC46B。EEPROM 必须在 4.35~5.25V 供电电源下,以 1Mb 时钟率的速率读取数据。很多 EEPROM 都可以达到上述要求。

- ◆ 阅读 EEPROM 的说明书,查找如何连接引脚 6 和引脚 7。一些设置这两个引脚为非连接状态,有些用这两个引脚来选择 16 位和 8 位 EEPROM 来实现测试功能。还有一些产片会将引脚顺序做 90°转换。鉴于上述原因,用户在选择和连接 EEPROM 时一定要格外小心。

- ◆ GC7232 可以和 MCU 共享一个 EEPROM,但是必须是在 GC7232 复位的时候,因为那时

EEPROM 的接口为三态。典型的配饰是用在 4 位的 MCU 的端口上。一位用来维持 GC7232 在上拉时的复位状态(引脚 RESET),其余三位与 EEPROM 的 EECS/EESK/EEDATA 连接,来实现在这个时间段对 EEPROM 的读写操作。一旦 MCU 对 EEPROM 进行读写操作,GC7232 的引脚 RESET 则为高电平来允许 GC7232 的自我配置和对 USB 的枚举。

## 11. USB 总线电源和本身电源配置

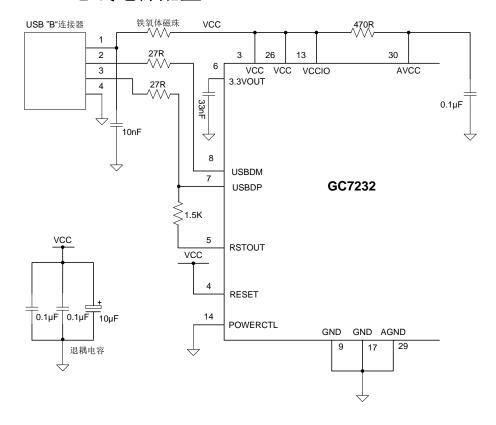

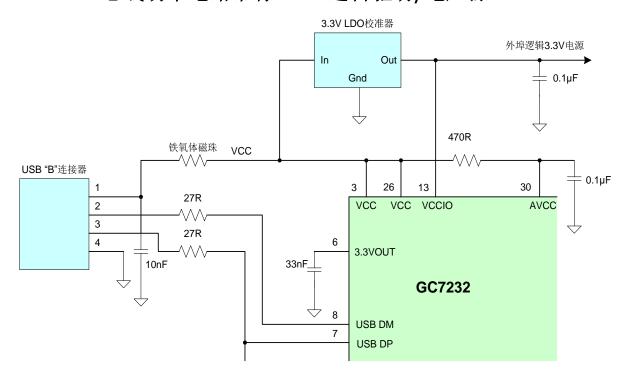

#### 11.1. USB 总线电源配置

- ◆ 上图展示了一个比较典型的 USB 电源配置。USB 总线器件通过 USB 总线获得电源。线面列 举出 USB 总线器件的基本规则:

- ▶ 插上电源时,器件必须能承受 100mA 以上的电流。

- ▶ 在 USB 暂停器件,器件必须能承受 500μA 以上的电流。

- ▶ 总线功率高功率器件(电流大于 100mA),应该使用 PWREN 引脚来维持插电时电流在 100mA 以下, USB 暂停时电流在 500uA 以下。

- ▶ 耗电量在 100mA 以上的功率器件不能直接插到 USB 总线插座。

- ➤ 不允许 USB 总线的器件大于 500mA。

- ◆ 引脚 14 (POWERCTL) 接地,这样器件会使用 USB 总线功率描述符。EEPROM 里的功率描述符必须编程的和器件相符合。

- ◆ 铁氧磁体珠和 USB 电源串联,防止来自器件的干扰和相关电路对 USB 和主机之间电缆的影响。铁氧磁体珠的值取决于电路总电流的需求。

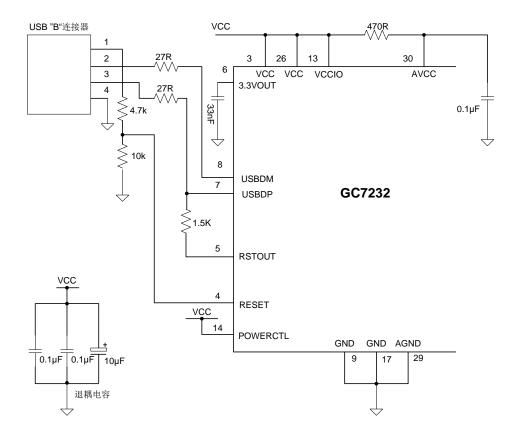

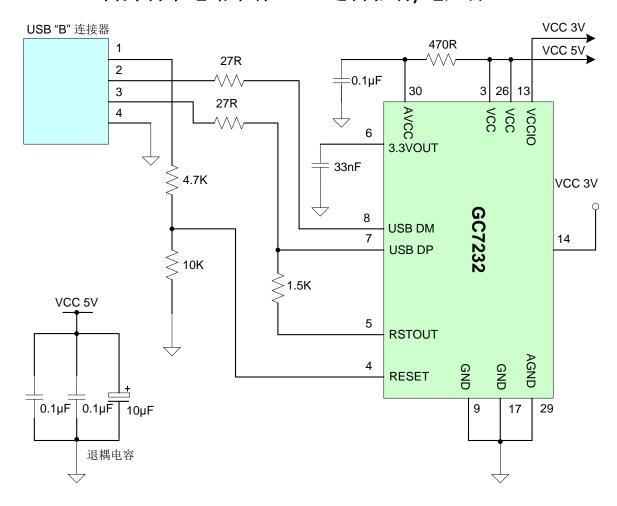

### 11.2. USB 自身功率配置

- ◆ 上图展示了典型的 USB 自身功率配置图。USB 从自身的供电电源获取功率,不会降低 USB 总线的电流。下面列举 USB 自身功率配置的基本规则:

- 当 USB 主机或者中心控制器功率下降时,自身功率器件不会导致 USB 总线电流下降。

- ➤ 在一般操作中和 USB 暂停时, 自身功率器件可以提供需要的电流。

- ▶ 自身功率器件可以和任意 USB 主机、所有总线以及 USB 自身功率中心一起使用。

- ◆ 引脚 14 (POWERCTL) 接高电平,来使得器件和 USB 总线功率描述符。EEPROM 中的 USB 总线描述符被编程为 0。

- ◆ 为了达到需求:

- ▶ USBDP 和 RSTOUT 之间连接 1.5k 电阻。但是 USB 总线通常控制 GC7232 引脚 4 (RESET)。当 USB 主机或者中心电源开启,RSTOUT 会通过 1.5k 的电阻将 USBDP 的电压上拉到 3.3V,这样识别全速 USB 器件。当主机或者中心电源关断,引脚 RESET 转为低电平,整个器件工作复位。RESET 低电平时 RSTOUT 也为低电平,所以在 USB 总线或者中心电源关断时,没有电流流过 1.5k 电阻。这个操作失败时,会导致部分 USB 总线和中心的控制器无规律的开启。

注意: 当 GC7232 复位时, UART 所有引脚都为三态。这些引脚和 VCCIO 接 200k 上拉电阻, 所以除非外部逻辑驱动,它们很容易升为高电平。

# 12. UART 接口配置

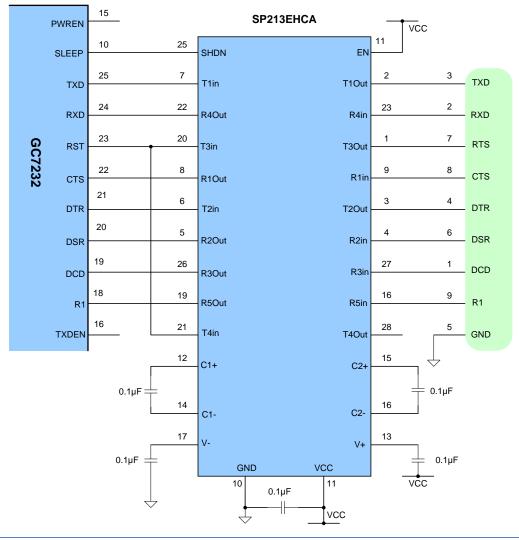

## 12.1. USB 与 RS232 转换器配置

- ◆ 上图展示了如何连接 GC7232 UART 和 TTL-RS232 转换器,实现了使用当下比较流行的串行 TTL "213"接法连接 USB 和 RS232 转换器。转换器件有 28 个引脚,其中包含了 4 个发射器和 5 个接收器,另外还有内建的电压转换器,实现从 5V VCC 电压到±9V 电压的转换,从而达到 RS232 串口对电压的要求。一个重要的特点是,引脚 SHDN 可以再 USB 暂停时,使整个器件为低电平,同事仅有弱小的静态电流。

- ◆ 上述图例中用的器件为 SP213EHCA,这个型号的器件可以实现与 RS232 在 500k 波特范围内的交流。如果需要的波特率比较低,那么兼容的芯片也可以使用,比如 Speix 的 SP213ECA, Maxim 的 MAX213CAI,还有模拟器件 ADM213E,这些器件都可以实现与 RS232 在 115,200范围内的交流。如需高波特率,Maxim 的 MAX3245CAI 可以实现 1M 波特。MAX3245 的引脚和 213 系列的不兼容,另外它的 SHDN 引脚高电平有效,所以必须与引脚 PWREN 连接。

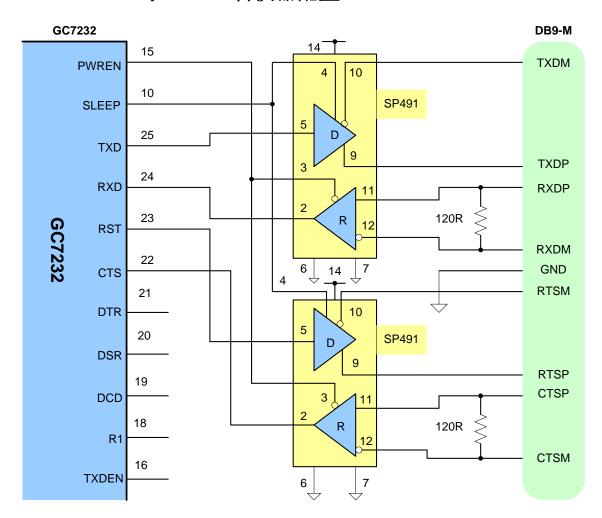

### 12.2. USB 与 RS422 转换器配置

◆ 上图展示了通过 GC7232 的 UART 接口和 TTL-RS422 串口的连接来实现 USB 和 RS422 转换的连接示意图。有很多器件都可以在这个应用中使用,上图选的器件是 Sipex 的 SP491,它可以同时驱动发射器和接收器。因为发射器是高电平有效,所以接 SLEEP 引脚。这样就

保证发射器和接收器在器件启动后都有效,在 USB 暂停时都无效。如果该设计是 USB 总线功率,那么需要用 P 沟道 MOS 管(由 PWREN 引脚来控制)连接到 SP491 的 VCC 线上,来确保 USB 500μA 的电流。

◆ SP491 可以实现 5M 波特的数据发送和接收,上图中,GC7232 和 SP491 连接可以实现 3M 波特。

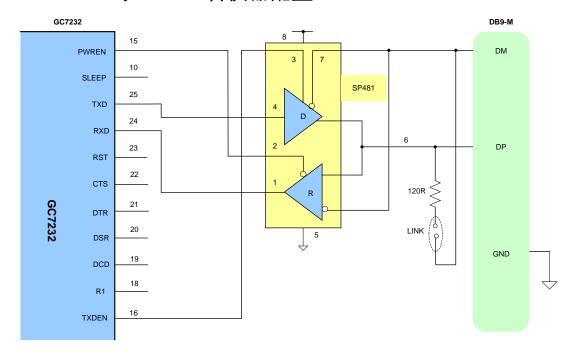

#### 12.3. USB 与 RS485 转换器配置

- ◆ 上图展示了通过 GC7232 的 UART 接口和 TTL-RS422 串口的连接来实现 USB 和 RS485 转换的连接示意图。这个例子使用的是 Speix 的 SP481, Maxim 和模拟器件出产的很多器件也可以拿来用。SP481 是 8 引脚 SOP 封装的 RS485 串口。可以分别开启发射器和接收器。发射器只能在 UART 发射符号时被启动,发射器连接到引脚 TXDEN 来实现这个功能。接收器低电平有效,所以接收器连接到 PWREN 引脚,这样在 USB 暂停期间,接收器不会工作。

- ◆ RS485 是一个多点网络。比如,多个器件可以通过 2 端点电缆连接来实现信息交流。RS485 电缆要求在每根电缆的端点结束。如果器件被放置在电缆的末端,上图中的"link"允许电缆结束。

- ◆ 在这个例子中,同一个器件完成了数据的发送和接收。这是 RS485 常见的特征,要求应用 软件从接收数据流移走需发射的数据。如果与 GC7232 相连接,那么这个动作可以有硬件来 完成:简单的修改电路原理图,使得 GC7232 的引脚 RXD 为 SP481 接收器的逻辑或,输出端 TXDEN 使用 HC32 或者类似的逻辑门。

# 13. LED 接口

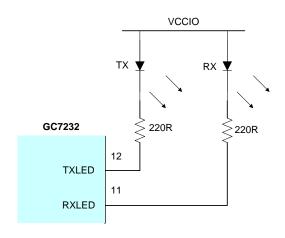

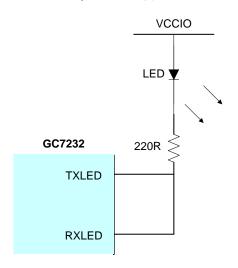

#### 13.1. 双 LED 配置

- ◆ GC7232 有 2 个 引 脚用于控制 LED 指示灯的状态,一个用来发射数据,另一个用来接收数据。 当开始发射或者接收数据,相应的引脚转为低电平来控制 LED 的状态。利用一次性数字计时器,这样一来,即使比较小的百分比的数据传输,对终端用户也是可见的。

- ◆ 上图为 2 个 LED 配置,一个用来发射数据,另一个用来接收数据。

## 13.2. 单 LED 配置

- ◆ 上图为单个 LED 指示器配置,将数据接收和收发捆绑在一起。可以比较灵活的来进行数据的接收或者发射。

- ◆ 另外一种应用是使用 3 引脚共阳极 3 色 LED 指示灯,根据接收数据和发射数据的对比来展

示不同的颜色。

注意: LED 接 VCCIO

# 14. 3.3V 逻辑接口

## 14.1. 总线功率电路带有 3.3V 逻辑驱动/电压源

- ◆ 上图展示 GC7232 如何连接 3.3V 逻辑器件。在上面例子中,一个分立的 3.3V 逻辑校准器与 USB 电源连接,为 GC7232 提供 3.3V 电源。VCCIO 与 3.3V LDO 逻辑校准器的输出连接, 这样可以一次引起 UART 接口输入输出引脚被 3.3V 电源驱动。对于 USB 总线功率电路,在 连接校准器时需要注意以下几点:

- ▶ 稳压器可以在输入电压为 4.35V 时输出 GC7232 所需要的(3.3V)电压。LDO(低压 差线性稳压器)是一个不错的选择。

- 》 为了保证 USB 在暂停时的电流在 500μA 以内,稳压器必须有足够小的静态电流。

- ◆ 目前市面上 MicroChip(Telcom)的 TC55 系列可以达到上述需求。这个系列的稳压器,可以提供 250mA 的电流,同时静态电流仅为 1uA。

- ◆ 在一些应用例子中,仅需要比较小的电流(<5mA),这时可以直接将 GC7232 的 VCCIO 引脚到引脚 3.3VOUT,来调用 GC7232 本身的稳压器。

注意: 在设计 USB 总线功率器件和 3.3V 逻辑接口时,需要强调 VCCIO 的 3.3V 电源要么来自 USB 总线(经过 LDO 稳压器),要么来自 3.3VOUT 引脚,除此之外不会有第三种方式。

## 14.2. 自身功率电路带有 3.3V 逻辑驱动/电压源

- ◆ 上图为 USB 3.3V 接口的自身电源设计。VCCIO 连接外部电源,为 GC7232 各个引脚提供 3.3V 的驱动电压,因此 VCCIO 可以和 3.3V 的 MCU 或者外部逻辑器件连接。这个设计中,使用的是本身的电源,所以不会影响到 USB 总线。在此类应用中,USB 暂停时没有特别需要注意的地方,因为器件没有从 USB 端口获取电源。

- ◆ 与总线电源设计一样,有些情况下需要的电流比较小,通过连接 GC7232 引脚 VCCIO 到引脚 3.3VOUT 来使用内部稳压器即可。

注意:在这个应用中,PWRCTL被上拉到 VCCIO,而不是 VCC。

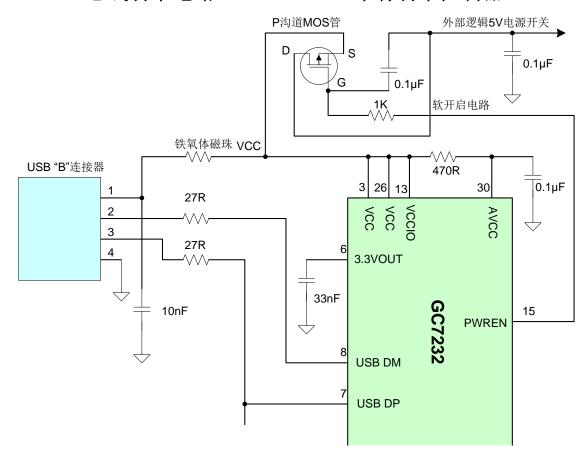

## 15. 电源开关

#### 15.1. 总线功率电路(<=100mA)带有功率控制器

- ◆ 为了保证 USB 暂停电流在 500μA 以内,USB 总线电源在 USB 暂停时必须终止供电。通过 检测引脚 PWREN,一些外部逻辑器件可以实现自我电源关断来保证低电流流过。对于那些 不能自我关断电源的逻辑器件,GC7232 提供了一个简单而有效的方式来实现外部逻辑器件 电源的关断。

- ◆ 上图展示了利用 P 沟道 MOS 管来控制外部逻辑电路的接法。可以选择仙童的 NDT456P, 美国整流器公司的 IRLML6402 以及同类器件。PMOS 的栅极连接 1k 电阻作为软开启电路, 连接 0.1μF 电容意在限流。没有软开启电路,瞬态功率溢出会导致 GC7232,USB 主机/中 心的控制器复位。这里的软开启电路允许的转换率约为 12.5v/ms,换句话说,输出电压由 GND 到 5V 需要 400μs。

- ◆ 另一种解决方案,可以用集成了软开启电路的开关电源来替代上述 MOS 管控制电路。可以 选择麦瑞半导体公司的 MIC2025-BL 或者同类兼容的产品。在设计连接时,以下是需要注意 的几点:

- ▶ 被控制的逻辑器件必须要有自身的复位电路,这样在暂停之后,它自身可以自动复位。

- ▶ GC7232 EEPROM 上设置暂停选项为下拉。

- > 对于 USB 高功率总线功率器件(USB 总线电流在 100mA~500mA),必须在 EEPROM 上设置器件功率消耗为最大值,EEPROM 上有高功率总线功率器件的描述符,包括该器件对功率的要求。

- ▶ 对于 3.3V 电源控制电路, VCCIO 不能被外部电路下拉(PWREN 从 VCCIO 获得 VCC)。 电源开关可以接在 3.3V 整流器和外部 3.3V 逻辑之间,也可以接在 GC7232 3.3OUT 引 脚和合适的电源 VCCIO。

# 16. 订货信息

| 产品型号             | 供货方式        |

|------------------|-------------|

| GC7232 <u>XX</u> | QFN32 引脚封装, |

|                  |             |

## 17. 文档修改记录

| 更改版本 | 更改内容 (每行一项) | 更改日期&更改者(简写)     |

|------|-------------|------------------|

| V11  | 规范文本格式      | 20130412 by anyh |

|      | 添加订货信息项     | 20130412 by anyh |

# 18. 文档信息

创建日期: 2012-05-31

作者: AYH